- 您现在的位置:买卖IC网 > Sheet目录892 > ZY8160G (Power-One)PROGBL CONVERT DC-DC 60A OUT THU

�� �

�

�

�ZY8160� 60A� DC-DC� Intelligent� POL�

�8V� to� 14V� Input� ?� 0.5V� to� 2.75V� Output�

�Data� Sheet�

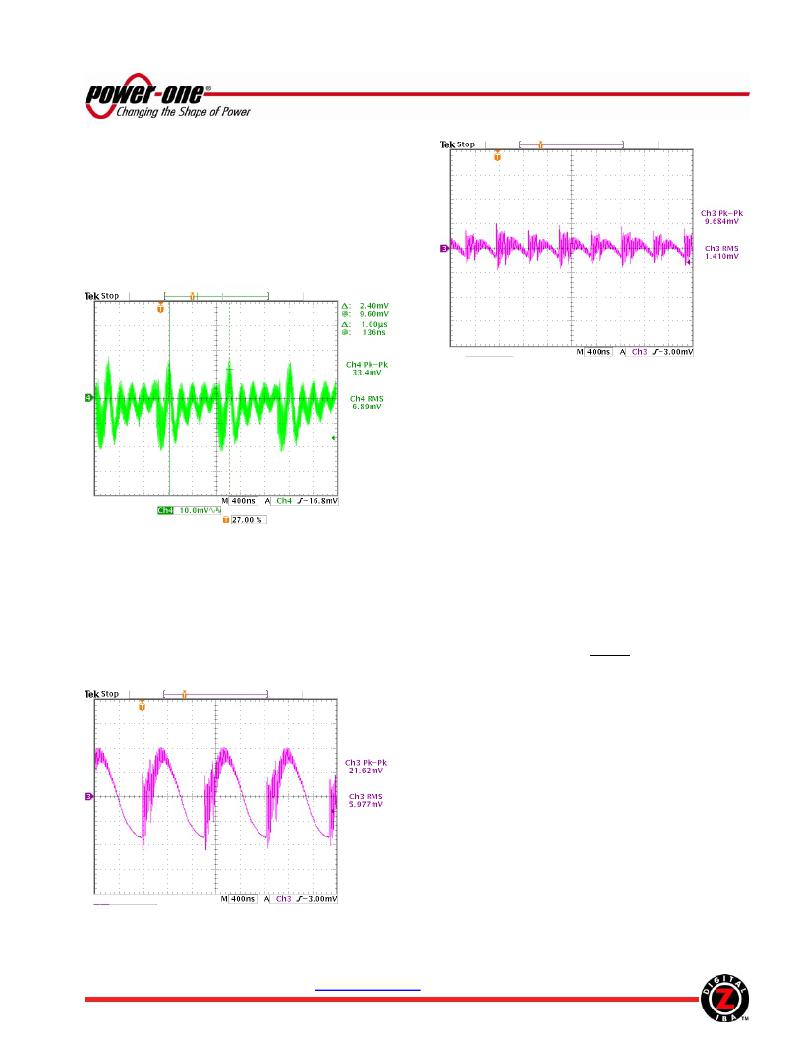

�Figure� 40� shows� the� input� voltage� noise� of� the� three-�

�output� system� with� programmed� interleave.� Instead�

�of� all� three� POLs� switching� at� the� same� time� as� in�

�the� previous� example,� the� POLs� V1,� V2,� and� V3�

�switch� at� 67.5°,� 180°,� and� 303.75°,� respectively.�

�Noise� is� spread� evenly� across� the� switching� cycle�

�resulting� in� more� than� 1.5� times� reduction.� To�

�achieve� similar� noise� reduction� without� the� interleave�

�will� require� the� addition� of� an� external� LC� filter.�

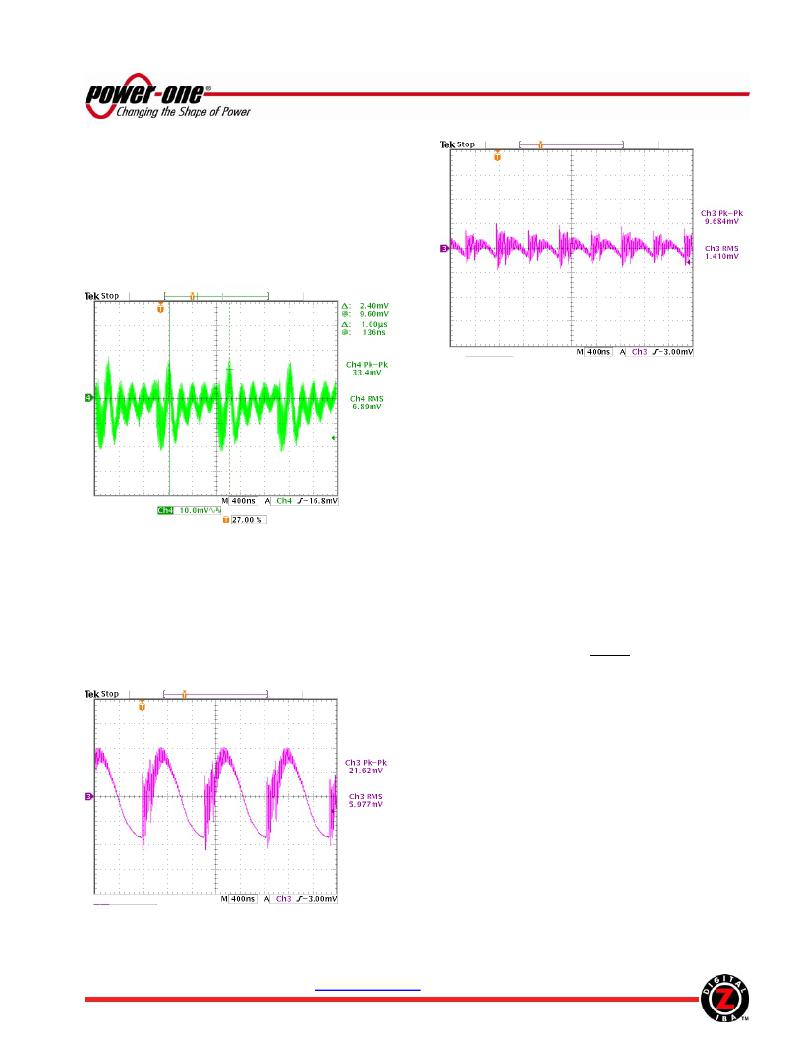

�Figure� 42.� Output� Voltage� Noise,� Full� Load,� 180� ?� Interleave�

�ZY8160� interleave� is� independent� of� the� number� of�

�POLs� in� a� system� and� is� fully� programmable� in�

�11.25� ?� steps.� It� allows� maximum� output� noise�

�reduction� by� intelligently� spreading� switching� energy.�

�Note� :� Due� to� noise� sensitivity� issues� that� may� occur� in� limited�

�cases,� it� is� recommended� to� avoid� phase� lag� settings� of�

�112.5� and� 123.75� degrees,� otherwise� false� PG� and/or� OV�

�indications� may� occur.�

�Figure� 40.� Input� Voltage� Noise� with� Interleave�

�DC� ?�

�,�

�Similar� noise� reduction� can� be� achieved� on� the�

�output� of� POLs� connected� in� parallel.� Figure� 41� and�

�Figure� 42� show� the� output� noise� of� two� POLs�

�connected� in� parallel� without� and� with� a� 180°�

�interleave,� respectively.� Resulting� noise� reduction� is�

�more� than� 2� times� and� is� equivalent� to� doubling�

�switching� frequency� or� adding� extra� capacitance� on�

�the� output� of� the� POLs.�

�8.4.3� Duty� Cycle� Limit�

�The� ZY8160� is� a� step-down� converter� therefore� V� OUT�

�is� always� less� than� V� IN� .� The� relationship� between�

�the� two� parameters� is� characterized� by� the� duty�

�cycle� and� can� be� estimated� from� the� following�

�equation:�

�V� OUT�

�V� IN� .� MIN�

�Where,� DC� is� the� duty� cycle,� V� OUT� is� the� required�

�maximum� output� voltage� (including� margining),�

�V� IN.MIN� is� the� minimum� input� voltage.�

�It� is� good� practice� to� limit� the� maximum� duty� cycle� of�

�the� PWM� controller� to� a� somewhat� higher� value�

�compared� to� the� steady-state� duty� cycle� as�

�expressed� by� the� above� equation.� This� will� further�

�protect� the� output� from� excessive� voltages.� The� duty�

�cycle� limit� can� be� programmed� in� the� GUI� PWM�

�Controller� window� or� directly� via� the� I� 2� C� bus� by�

�writing� into� the� DCL� register� shown� in� Figure� 43.�

�Figure� 41.� Output� Voltage� Noise,� Full� Load,� No� Interleave�

�ZD-01674� Rev.� 1.2,� 02-Jul-10�

�www.power-one.com�

�Page� 24� of� 30�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

0006660012

CABLE 28AWG 148MM RED

0006660013

CABLE 28AWG 300MM RED

002679-000

CABLE 22AWG TWISTED

0082226102

RIB CBL .100 100RL TIN 2POS

0082226104

RIB CBL .100 100RL TIN 4POS

0082226115

RIB CBL .100 100RL TIN 15POS

0192520124

TIE 4 INCH 18LB NATURAL

0192520125

TIE 6.1 INCH 18LB NATURAL

相关代理商/技术参数

ZY8160G-Q1

制造商:Power-One 功能描述:

ZY8160G-R1

功能描述:DC/DC转换器 8-14Vin 60A(max) 0.5-2.75Vout 29mA RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸:

ZY82

制造商:FAGOR 功能描述:FAGOR S9G7A 制造商:General Instruments 功能描述:Zener Diode, Two Terminal, 82 Volt, 6.7%, DO-15

ZY82B

制造商:DIOTEC 制造商全称:Diotec Semiconductor 功能描述:Silicon Power Z-Diodes (non-planar technology)

ZY82GP

制造商:未知厂家 制造商全称:未知厂家 功能描述:2 W Glass Passivated Zener Diode

ZY8V2GP

制造商:未知厂家 制造商全称:未知厂家 功能描述:2 W Glass Passivated Zener Diode

ZY9.1

制造商:DIOTEC 制造商全称:Diotec Semiconductor 功能描述:Silicon-Power-Zener Diodes (non-planar technology)

ZY9.1V

制造商:CDIL 制造商全称:Continental Device India Limited 功能描述:SILICON GLASS PASSIVATED 2.0 WATT ZENER DIODES